http://www.aimspress.com/

AIMS Materials Science, 2(4), 510-529. DOI: 10.3934/matersci.2015.4.510 Received date 16 May 2015, Accepted date 03 November 2015,

Published date 24 November 2015

# Research article

# Towards low-voltage organic thin film transistors (OTFTs) with solution-processed high-k dielectric and interface engineering

Yaorong Su 1,\*, Weiguang Xie 2, and Jianbin Xu 1

- Department of Electronic Engineering and Materials Science and Technology Research Centre, The Chinese University of Hong Kong, Shatin, Hong Kong SAR, China

- <sup>2</sup> Siyuan Laboratory, Department of Physics, Jinan University, Guangzhou, Guangdong, 510632, P. R. China

- \* Correspondence: Email: yrsu@ee.cuhk.edu.hk or yrsucuhk@gmail.com.

**Abstract:** Although impressive progress has been made in improving the performance of organic thin film transistors (OTFTs), the high operation voltage resulting from the low gate capacitance density of traditional SiO<sub>2</sub> remains a severe limitation that hinders OTFTs' development in practical applications. In this regard, developing new materials with high-*k* characteristics at low cost is of great scientific and technological importance in the area of both academia and industry. Here, we introduce a simple solution-based technique to fabricate high-*k* metal oxide dielectric system (ATO) at low-temperature, which can be used effectively to realize low-voltage operation of OTFTs. On the other hand, it is well known that the properties of the dielectric/semiconductor and electrode/semiconductor interfaces are crucial in controlling the electrical properties of OTFTs. By optimizing the above two interfaces with octadecylphosphonic acid (ODPA) self-assembled monolayer (SAM) and properly modified low-cost Cu, obviously improved device performance is attained in our low-voltage OTFTs. Further more, organic electronic devices on flexible substrates have attracted much attention due to their low-cost, rollability, large-area processability, and so on. Basing on the above results, outstanding electrical performance is achieved in flexible devices. Our studies demonstrate an effective way to realize low-voltage, high-performance OTFTs at low-cost.

**Keywords:** high-k; solution processed; low voltage; OTFTs; interface engineering; flexible

#### 1. Introduction

During the past decades, rapid progress has been achieved in both the designing of novel organic semiconducting materials and the optimization of device fabrication techniques for organic thin film transistors (OTFTs) due to their potential applications in low-cost and flexible consumable electronics, such as such as RFID tags, flat panel displayers, and portable electronics [1–4]. However, the high operation voltage resulting from intrinsically low charge carrier mobility of organic semiconductors and the small gate capacitance density of traditional SiO2 remains a severe limitation that hinders their development in the market of commercial electronics [5]. This issue can be addressed through increasing the capacitance density of the gate dielectrics  $(C_i)$  by means of either increasing the dielectric constant (k) or decreasing the thickness (d) ( $C_i = \varepsilon_0 k/d$ ). Practically, using high-k dielectrics instead of ultra-thin dielectrics is a promising choice, and much research interest has been devoted into this area. Metal oxides are important members of high-k dielectrics. Traditional fabrication routes for high-k metal-oxide dielectrics, such as atomic layer deposition [6], radio-frequency magnetron sputtering [7] and chemical vapor deposition [8], require expensive, high-vacuum equipment, and are time consuming to produce functioning layers. Therefore, it is of significant importance to develop a low-temperature, solution-based technique for the fabrication of high-k metal-oxides as gate dielectrics, in order to turn OTFTs into more reliable applications for low-cost, large-area devices.

Besides the development in synthesizing high-performance organic semiconductors and the gate dielectrics, much effort has been devoted to improve the device performance by optimizing the device performance through interface engineering [9-12]. Basically, two interfaces, i.e. organic semiconductor/dielectric interface and source-drain (S/D) electrode/organic semiconductor interface, are involved in the processes of charge transportation and injection/extraction. The native high-k metal oxide dielectric surface usually contains hydroxyl groups (OH<sup>-</sup>), which act as defect sites, trapping charge carriers in the channel or inducing undesired charge carriers into the channel [13,14,15]. This issue can be overcome by introducing a self-assembled monolayer (SAM) at the interface between dielectrics and organic semiconductors, which can simultaneously passivate the defects and modify the oxide surface, resulting in enhanced device performance [16,17,18]. Among diverse SAMs, phosphonic acid headed alkylate has shown great advantages of readily chemisorbed onto metal-oxide surface [19,20,21] high thermal stability (~ 400 °C) [22], and other unique merits including better stability to moisture, less tendency of self-aggregation and unlimited by the densed surface hydroxyl groups [23]. For the interface between S/D electrode/semicondcutor, one should be aware of two different circumstances. For efficient hole injectoin, an electrode material with enough high work function  $(W_F)$  that can be aligned with the highest occupied molecular obital (HOMO) of organic semiconductor is preferred. On the other hand, for efficient electron injection, the  $W_F$  of the electrode material should be low enough to align with the lowest unoccupied molecular orbital (LUMO) of organic materials. Moreover, to synchronize with the already established Si based microelectronic industry, it would be easier to realize large scale production of organic electronic devices if Cu can be used as the S/D electrodes of OTFTs. However, Cu is generally believed to be unsuitable as the S/D electrodes material due to its low work function (4.2 eV) [24], which results in large injection barrier when contacting with most p-type and n-type organic semiconductors, thus deteriorating device performance. To address this dilema, chemical modifications at the interface of Cu and organic semiconductor have attracted much attention in order to improve the device performance [25,26].

In addition, the inherent mechanical flexibility and low-temperature processibility of organic semiconductors stimulate the attempts of integration of OTFTs with bendable substrates, which is of great technical significance because they are fundamental building blocks of most practical electronic devices. Furthermore, to realize printability in future organic electronics industry, it is necessary to develop low-temperature, solution-processible dielectric materials that can be compatible with the high-throughput production, such as roll-to-roll processing.

In this paper, we will give a brief review of our recent research results on solution-processed high-k metal-oxide dielectric and the related low-voltage OTFTs. At first, a sol-gel based high-k metal-oxide dielectric will be introduced, which can then be used effectively to realize low-voltage operation of OTFTs [27,28,29]. Secondly, highly improved device performance using low-cost Cu as S/D electrodes for both p- and n-type organic semiconductors is demonstrated through interface engineering [30,31]. Finally, based on the above findings, flexible pentacene OTFTs on polyimide (PI) substrates are successfully fabricated with excellent device performance [32]. Our results demonstrate a simple and feasible route to fabricate high-performance OTFTs with solution-processed dielectric and low-cost electrode material, which is of great technical importance to realize large-scale application of organic electronics.

## 2. Materials and Method

All the chemicals used in this paper are bought from Aldrich without further clarification. Titanium oxide (TiO<sub>x</sub>) sol was prepared by dissolving titanium (IV) isopropoxide (TIP) (Ti(OC<sub>3</sub>H<sub>7</sub>)<sub>4</sub>, 99.99%) into a mixture of methanol and acetic acid in a concentration of about 0.1 mol/L, and then vigorously stirred for 24 h in ambient conditions. Aluminum oxide (Al<sub>2</sub>O<sub>v</sub>) sol was prepared by dissolving aluminum nitrate nonahydrate (Al(NO<sub>3</sub>)<sub>3</sub>•9H<sub>2</sub>O, 99.99%) into 2-methoxylethanol in a concentration of about 0.5 mol/L and then stirred for 12 h in ambient conditions. The TiO<sub>x</sub> layer was deposited by spin-coating the TiO<sub>x</sub> sol onto the cleaned n<sup>++</sup>-Si substrates at 5000 r/min for 40 s, followed by baking at 200  $\pm 5$  °C for 5 min to ensure the hydrolyzation and decomposition of the precursor. Subsequently, the Al<sub>2</sub>O<sub>v</sub> layer was deposited by spin-coating the Al<sub>2</sub>O<sub>v</sub> sol onto the cooled TiO<sub>x</sub>-coated substrates and then baked at the same condition as that of TiO<sub>x</sub>. The obtained double layer Al<sub>2</sub>O<sub>v</sub>/TiO<sub>x</sub> is referred to ATO for short hereafter. For ATO deposited on flexible PI substrates, the spin-coating condition is the same as that on n<sup>++</sup>-Si substrates. Prior to ATO deposition, 5 nm Cr and 20 nm Au was vacuum deposited successively on PI substrates under a vacuum of  $3 \times 10^{-4}$  Pa. For SAM modification, the as prepared ATO substrates were immediately immersed in an octadecylphosphonic acid (ODPA) solution (5 mmol/L in isopropanol) for 20 h, followed by a 48 h curing at 145 °C in vacuum, and then washed by isopropanol ultrasonically for 6 min and blown dry by N<sub>2</sub> gas for use.

Bottom-gate top-contact (BGTC) OTFTs were fabricated by thermally deposition of 30 nm organic semiconductors onto the substrates with temperatures of 180 °C for copper phthalocyanine (CuPc), 60 °C for pentacene and and 110 °C for C60, respectively, followed by deposition of S/D electrodes through shadow mask. For pentacene TFTs, the *in-situ* modified Cu electrodes (*M*-Cu) was formed by firstly deposited onto the pentacene layer under a gradient deposition pressure from  $5 \times 10^{-3}$  Pa to about  $3 \times 10^{-4}$  Pa, and then 10 nm Au was deposited onto the above *M*-Cu without breaking the chamber vacuum. For C<sub>60</sub> TFTs, a branched polyethylenimine (PEI, M<sub>W</sub> =

25000)/methanol solution was spin-coated onto the C60 film before Cu electrodes deposition.

The electrical characteristics of the  $C_{60}$  OTFTs were measured by Keithley 4200 SCS. The frequency-dependent capacitance of the dielectrics was measured by HP 4284A in a frequency range of 20 Hz-100k Hz. The morphologies of the thin films were characterized by atomic force microscopy (AFM, Nanoscope IIIa) in tapping mode. The surface potential was recorded by KPFM method using Pt coated tips. The X-ray diffraction (XRD) patterns were obtained on an X-ray diffractometer (Simens, D5000) using Cu  $K\alpha$  radiation ( $\lambda$  = 0.154 nm) at a scan rate of 0.02° 20/s. The two-dimensional grazing incidence X-ray diffraction (GIXD) pattern was obtained at beamline BL14B1 ( $\lambda$  = 1.24 Å) of the Shanghai Synchrotron Radiation Facility with an incident angle of 0.15°.

#### 3. Results and Discussion

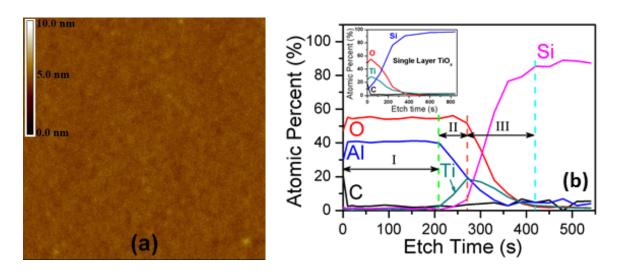

Figure 1a shows the tapping mode AFM image of the ATO. As seen, the ATO exhibits a homogenous and smooth surface with a root mean square (RMS) roughness value of  $\sim 0.22$  nm in an area of 5  $\mu$ m  $\times$  5  $\mu$ m, as smooth as that of the n<sup>++</sup>-Si substrate with 300 nm SiO<sub>2</sub> (RMS  $\sim 0.19$  nm), and no obvious surface defects and pinholes are observed. Figure 1b shows the atomic composition profiles of O, Al, C, Ti, and Si as a function of etching time obtained from the bilayer Al<sub>2</sub>O<sub>y</sub>/TiO<sub>x</sub>. As seen, the atomic ratio of Al to O in region I is about 2:2.7, giving an y value of 2.7. With increasing etching time, the intermixing layer containing Al<sub>2</sub>O<sub>y</sub> and TiO<sub>x</sub>, which can be observed in region II. Beneath region II, a more complex intermediate layer containing Al, Ti, Si, and O, marked as region III, is observed. The total thickness of the bilayer Al<sub>2</sub>O<sub>y</sub>/TiO<sub>x</sub> is estimated to be 45 nm (measured by AFM). The inset of Figure 1b shows the depth profiles of atomic composition obtained from a 12 nm thick, single layer TiO<sub>x</sub>. In the case of single layer TiO<sub>x</sub>, the atomic ratio of Ti and Si to O is smaller than 2, suggesting that some oxygen vacancies exist in the transition layer.

Figure 1. (a) AFM image and (b) XPS depth profile of ATO; the inset of (b) shows the XPS depth profile of single layer  $TiO_x$ .

To characterize the electrical properties of the solution-processed dielectric, we fabricate an Au/ATO/n<sup>++</sup>-Si (MIM) sandwiched structure and test its current-voltage and capacitance-frequency

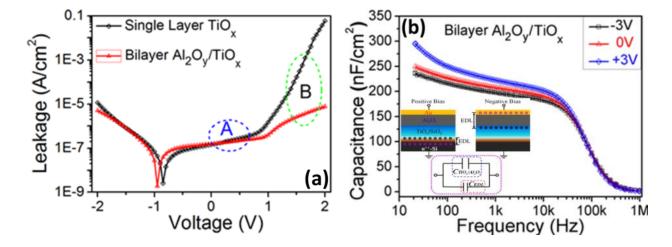

characteristics. Figure 2a shows the typical leakage current density versus bias voltage plots of a single layer TiO<sub>x</sub> and ATO. The asymmetrical leakage of single layer TiO<sub>x</sub> is likely due to the zero conduction band offset at the Si/TiO<sub>x</sub> interface [8] and the different work function of Si and Au, as can be seen from Figure 2a. After deposition of the Al<sub>2</sub>O<sub>v</sub> layer, the leakage current was reduced by 4 orders of magnitude under positive bias of +2 V. The reduction of leakage is due to the blocking of electron conduction path by the Al<sub>2</sub>O<sub>v</sub> layer. In addition, two distinct regions can be observed in both single layer and bilayer dielectrics, as noted with A and B. Similar phenomena have been extensively studied by Mahapatra et al, and according to their theory, the conduction in region A is governed by a charge hopping process and the conduction in region B is dominated by both Proole-Frenkel emission and trap assisted tunneling processes [18]. Figure 2b exhibits the frequency dependence of capacitance density for the MIM structure under different bias voltages. For single layer TiO<sub>x</sub>, under a bias voltage of 0 V, the total capacitance density is  $\sim 850 \text{ nF/cm}^2$  at 20 Hz, and an equivalent k value of about 12 can be obtained. As for the bilayer Al<sub>2</sub>O<sub>v</sub>/TiO<sub>x</sub>, capacitance density is reduced owing to the introduction of another capacitor (i.e. Al<sub>2</sub>O<sub>v</sub>) in series. In addition, the observed voltage dependence capacitance density can be attributed to the variation of space charge distribution, i.e., the redistribution of oxygen vacancies in the film driven by the applied voltages [19]. This positively charged oxygen vacancy accumulation layer induces additional electrons at the bottom electrode, forming an "electric double-layer" (EDL) capacitor. For better understanding the voltage and frequency dependent capacitance density, a simple model with equivalent circuit is proposed in the inset of Figure 2b. Under an AC bias with sufficiently low frequencies, the oxygen vacancies will have enough time to respond to the bias change and go back and forth in the vicinity of the space charge layer, which can be viewed as a macroscopic dipole oscillating with the field. The lower the frequency is, the larger the distance of oscillation is, and ultimately giving rise to larger the capacitance density.

Figure 2. (a) Leakage current density and (b) frequency dependent capacitance density characteristics of ATO; the inset of (b) is the proposed EDL model and equivalent circuit.

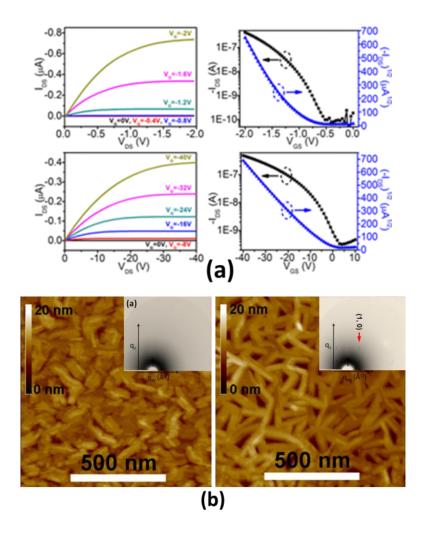

To demonstrate the effectiveness of our solution-processed ATO dielectric, bottom-gate, top-contact (BGTC) CuPc OTFTs with Au S/D electrodes are fabricated. The upper two figures of Figure 3a show the output and transfer curves of a representative CuPc OTFT. Due to the high

capacitance of ATO, the device can work effectively at operation voltages as low as -2 V. Clear linear and saturation regions can be observed from the output curves. From the transfer curve, the  $\mu$ ,  $V_T$ , on/off ratio, and SS are estimated to be 0.15 cm<sup>2</sup>/Vs, -1.1 V,  $5 \times 10^3$ , and 232 mV/dec, respectively. Comparatively, the 300 nm SiO<sub>2</sub> based CuPc device is also fabricated, and the obtained  $\mu$ ,  $V_T$ , on/off ratio and SS are  $2.8 \times 10^{-3}$  cm<sup>2</sup>/Vs, -6.0 V,  $10^3$  and 5.9 V/dec, respectively, under a high voltage of -40 V, as shown in the lower part of Figure 3a. Apparently, the device on ATO exhibits much higher performance than that on 300 nm SiO<sub>2</sub>. The electronic property of OFETs can be influenced by several aspects, such as dielectric surface property, organic layer crystal structures, and

Figure 3. (a) Output and transfer curves of CuPc OTFTs on ATO (the upper two) and 300 nm  $SiO_2$  (the lower two), (b) AFM image so 2.4 nm CuPc on ATO (left) and 300 nm  $SiO_2$  (right); the inset in (b) corresponds to their respective GIXD pattern.

semiconductor-dielectric interface characteristics. AFM and XRD studies reveal that the ATO and SiO2 have similar surface roughness, and the CuPc deposited on both dielectric give the same crystal structure. To get a deeper insight into the difference in device performance, the interface between CuPc and dielectrics are characterized, and the results are shown in Figure 3b. As seen, when deposited on SiO<sub>2</sub>, the growth of CuPc molecules exhibits the Stranski-Krastanov mode [33], which occurs when the interaction between the molecules and the substrates are stronger than that between

the molecules [34]. On the other hand, when deposited on ATO, the growth of CuPc molecules can be described by the Volmer-Veber growth mode [33], in which the deposited molecules are more strongly bonding to each other than to the substrate [34]. In addition, the insets of Figure 3b show the GIXD patterns of 2.4 nm CuPc on both dielectrics. No diffraction peak is found in the CuPc on SiO<sub>2</sub>, indicating that the amorphous in-plane structure for the first several monolayers. On the other hand, a clear diffraction peak noted as (1,0) can be observed from the pattern of the CuPc film on ATO (indicated by the red arrow), revealing a crystalline structure of the first several monolayers of CuPc. The ordered in-plane structure and the interconnected network of CuPc on ATO thus account for the highly enhanced device characteristics of our devices, because the charge transport at the conducting channel is mainly located at the first several monolayers at the interface [35,36].

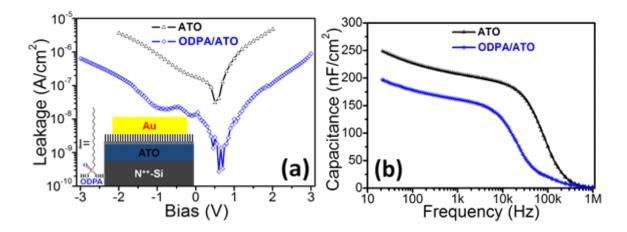

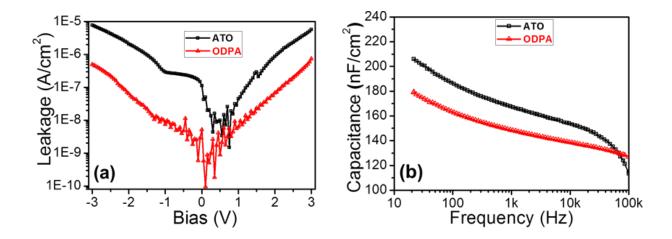

We have introduced the low-temperature (~ 200 °C) solution-processed high-k ATO dielectric system, and the CuPc TFTs with this gate dielectric show good electrical performance under an operation voltage as low as -2 V. However, native oxide dielectric surface usually contains hydroxyl groups (OH<sup>-</sup>), which act as defect sites, trapping charge carriers in the semiconductor/dielectric interface or inducing undesired charge carriers into the interface [13,14,15]. To further improve the device performance, surface modification is employed to optimize the interface property. Here we use ODPA to modify the surface of ATO. Figure 4 shows the leakage and frequency dependent capacitance characteristics ODPA modified ATO (ODPA/ATO) and bare ATO. As shown in Figure 4a, after ODPA modification, the leakage current density can be significantly suppressed by more than one order of magnitude under a bias of 2 V. The decrease in leakage current density indicates the formation of densely packed ODPA molecules on the surface of alumina in ATO. The static contact angle of DI water on ODPA/ATO is about 110°, while that on bare ATO is about 35°, further confirming the formation of high quality SAM [37]. The  $C_i$  of ODPA/ATO is 200 nF/cm<sup>2</sup>, while that of bare ATO is 250 nF/cm<sup>2</sup>, as can be seen from Figure 4b. The low leakage, large contact angle (low surface energy), and high capacitance density of the ODPA/ATO system endows it with suitability for high-performance low-voltage OTFTs.

Figure 4. (a) leakage and (b) frequency dependent capacitance density of ATO and ODPA/ATO.

Besides the dielectric properties, the choices of S/D electrode materials are also crucial in achieving high-performance devices. Generally speaking, for p-type organic semiconductors, the electrodes need to have high enough WF to align with the HOMO of the semiconductor. Au is the

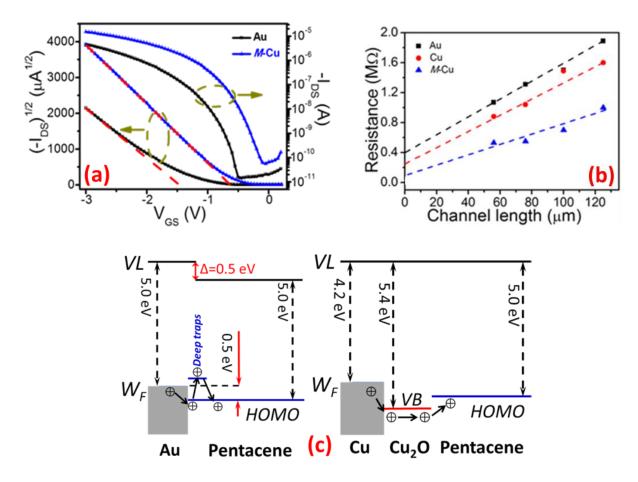

most widely used S/D electrode material for pentacene TFTs because of its inherently high work function, good conductivity and environmental stability. However, the high cost of Au hinders its use in realistic applications. Furthermore, during thermal deposition, the severe diffusion of Au into pentacene film results in high resistive grain boundaries and forms interface dipoles by doping the upper layer pentacene, and thus deteriorating the device perofrmance [38–41]. These unfavorable issues can be overcome by using in-situ modified low-cost Cu (M-Cu) as S/D electrodes, in which the Cu atoms are in-situ oxidized by residual oxygen species in the chamber at low vacuum atmosphere. The CuO<sub>x</sub> formed in the interface of Cu and pentacene is believed to function as a modification layer owing to its high valence band. To verify the validity of M-Cu S/D electrodes, the pentacene TFTs are fabircated the their electrical performance is shown in Figure 5a. Owing to the high capacitance density of the ODPA/ATO (200 nF/cm<sup>2</sup>), the devices worked very well under a low gate voltage of -3 V. For the device with M-Cu electrodes, the  $\mu$  and  $V_T$  are estimated to be 1.0 cm<sup>2</sup>/Vs, 156 mV/dec and -0.62 V, respectively. In comparison, for the device with Au electrodes, the  $\mu$  and  $V_T$  are determined to be 0.71 cm<sup>2</sup>/Vs and -1.4 V, respectively. As clearly seen, the device with M-Cu electrodes exhibits much higher performance as compared to that with Au electrodes. Because both devices were fabricated under the same condition, excepting the S/D electrodes, it is plausibly to ascribe the above observations to the interaction between electrode and organic semiconductor. To clarify the relationship between electronic performance of devices and S/D electrodes, we estimate the contact resistance  $(R_C)$  with the transfer line method (TLM) in the linear region [42]. Figure 5b shows the dependence of total resistance on channel length of devices with different electrodes, and  $R_C$  is obtained from the intercept by extrapolating the resistance line to the zero channel length. For Au electrodes, the  $R_C$  is estimated to be about 0.41 M $\Omega$ . For M-Cu electrodes, on the other hand, the  $R_C$  is drastically reduced, estimated to be about 0.11 M $\Omega$ . During thermal deposition, hot Au atoms usually diffuse into the pentacene film, thus resulting in high resistive grain boundaries and forming interface dipoles by doping the upper layer pentacene [41,43,44]. However, when using M-Cu as S/D electrodes, Cu atoms are oxidized by residual oxygen species in the chamber due to the low vacuum atmosphere. As a result, a thin layer of CuOx is in-situ formed at the initial stage of thermal deposition instead of pure Cu. XPS results revealed that the interface CuOx is mainly composed of Cu<sub>2</sub>O. Cu<sub>2</sub>O is a widely studied p-type semiconductor with valence band (VB) position locating around 5.4 eV [45], which is well aligned with the highest occupied molecular orbital (HOMO) of pentacene (5.0 eV) [46]. Consequently, the *in-situ* oxidized CuO<sub>x</sub> layer in M-Cu electrodes can act as an effective hole-injection layer, resulting in optimized electrode/pentacene contact, and hence improving the device performance. To better understand the mechanism, the band diagram of different electrode materials are given in Figure 5c. For Au electrodes (left part), an typical value of interface dipole ( $\Delta$ ) of 0.5 eV is adopted [41]. Due to the physical and chemical damage caused in the interface of Au/pentacene, some deep trap sites are induced. When M-Cu is used as the S/D electrodes (right part), the thin layer of Cu<sub>2</sub>O in the interface serves as a effective hole-injection layer.

High-performance p-channel pentacene OTFTs have been demonstrated with low-cost Cu S/D electrodes through interface engineering. However, from the point of view of integrated circuits design basing on the industrial complementary metal oxide semiconductor (CMOS) technique, both p-channel and n-channel OTFTs are desired. For efficient electron injection into n-type organic semiconductors, the work function  $(W_F)$  of the electrode should be low enough to align with the lowest unoccupied molecular orbital (LUMO) of organic materials, thus lowering the electron

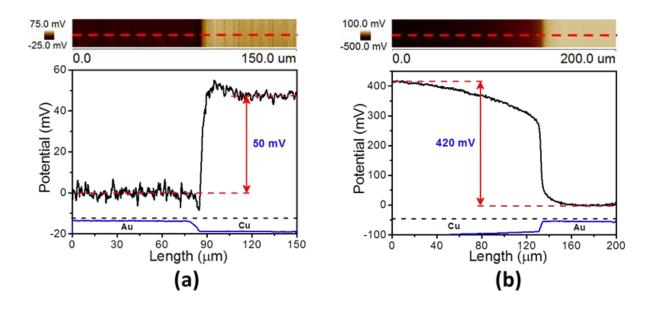

injection barrier and forming the Ohmic contact. Zhou et al. reported that the  $W_F$  of conductors, such as Au, Ag and ITO, can be substantially reduced upon simply spin-coating a thin layer of polyethylenimine ethoxylated (PEIE) or branched polyethylenimine (PEI), which containing aliphatic amine groups, and obviously improved device performance was observed by using the modified conductors as electrodes owing to the enhanced electron injection at the electrode/semiconductor interface [47]. Here, as inspired by the same idea, we employ PEI to modify Cu to see whether it can be used as an effective S/D electrodes for n-type organic semiconductors. To evaluate the effect of PEI modification on the surface performance of Cu, KPFM was used to record the  $W_F$  variation by measuring the contact potential difference (CPD) between the sample and the reference Au film. Before measurements, the  $W_F$  of Au is calibrated by freshly peeled highly ordered pyrolytic graphite (HOPG) with a known  $W_F$  of 4.6 eV [48]. The calibration reveals that the  $W_F$  of Au is determined to be 4.7 eV, which is in good agreement with those reported values due to existence of surface contaminates when exposing to ambient atmosphere [49,50]. Figure 6 gives the comparison of KPFM images of Cu before and after PEI modification. As seen in Figure 6a, the surface potential of thermally deposited Cu is about 50 mV higher than that of Au, indicating that the W<sub>F</sub> of Cu is 4.65 eV, which is consistent with the reported values [51,52]. Surprisingly, after PEI

Figure 5. (a) Transfer curves of pentacene OTFTs with Au and M-Cu S/D electrodes, (b) transfer line method (TLM) polts of pentancene TFTs with different S/D electrodes and (c) schematic energy diagrams of Au/pentacene (left) and M-Cu/pentacene (right).

modification, the CPD between Au and the modified Cu increases to about 420 mV, denoting a drastic decrease in  $W_F$  of Cu to 4.28 eV, as shown in Figure 6b. It is known that the amine group has a strong electron donating feature, and there will be a charge-transfer interaction between amine group and the Cu surface, thus resulting in a reduced  $W_F$  [47,53]. On the other hand, the intrinsic molecular dipole within the polymer may also contribute to the decreased  $W_F$  of Cu [54,55].

Figure 6. KPFM results of Cu before (a) and after PEI modification (b); the lower parts give the topography of each device.

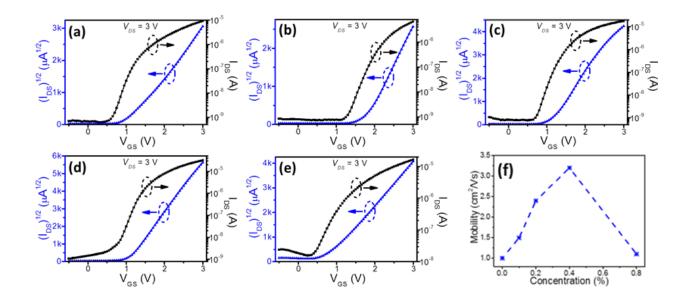

Figure 7 gives the transfer characteristics of top-contact C<sub>60</sub> based OTFTs fabricated on the ODPA/ATO using Cu and PEI modified Cu as S/D electrodes. As seen, all devices can work perfectly under a gate voltage  $(V_{GS})$  as low as 3 V due to the high capacitance density of the gate dielectric. When Cu is used as S/D electrodes, the electron mobility ( $\mu_e$ ) is determined to be 1.0 cm<sup>2</sup>/Vs. Surprisingly, after modifying Cu with 0.1% (wt%) PEI solution, the  $\mu_e$  increases to about 1.5 cm<sup>2</sup>/Vs, indicating that PEI modification can effectively enhance the device performance. Noting that methanol is used as the solvent in our experiment, which might also impact the resultant device property. To find out the dominant influencing factor, a control sample with only methanol spin-coating on the surface of C<sub>60</sub> before the deposition of Cu S/D electrodes is also fabricated for comparison. The electrical performance of the control sample, however, shows a slight degradation (with  $\mu_e$  of 0.7 cm<sup>2</sup>/Vs) against the above PEI modified one, which can be due to the residue of polar methanol molecules in the C<sub>60</sub> film acting as the charge trapping centers for both holes and electrons [56]. The above results confirm that the improving in device performance is resulted from the PEI modification. Further studies reveal that the device performance also strongly depends on the concentration of PEI solution. As can be seen from Figure 7c, when 0.2% PEI solution is used, the  $\mu_e$ increases to about 2.4 cm<sup>2</sup>/Vs, which is obviously higher than that of the device with Cu S/D electrodes. With further increase the concentration of PEI solution, the  $\mu_e$  reaches the peak value of about 3.2 cm<sup>2</sup>/Vs at 0.4% and then followed by a decline to about 1.1 cm<sup>2</sup>/Vs at 0.8%, as shown in Figure 7d and e. For better understanding, the relationship between electron mobility of C<sub>60</sub> TFTs and the PEI concentration is plotted in Figure 7f. As seen, the mobility increases monotonously with the concentration of PEI in the beginning, and then reaches the highest value at 0.4%. After that, a rapid depression is evidenced with further increasing the concentration to 0.8%. As far as we know, the obtained electron mobility value of  $3.2 \text{ cm}^2/\text{Vs}$  is the highest one achieved in C<sub>60</sub> TFTs basing on ODPA modified dielectrics [57,58,59].

Figure 7. Transfer characteristics of  $C_{60}$  OTFTs using Cu (a) and PEI modified Cu with various concentrations as S/D electrodes, (b), (c), (d) and (e) correspond to concentrations of 0.1%, 0.2%, 0.4% and 0.8%, respectively; (f) plot of PEI concentration dependent mobility.

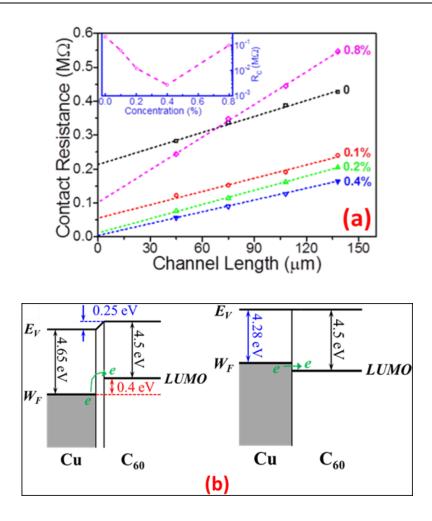

To further explore the relationship between PEI modification and the device performance, the relationship between  $R_C$  against PEI concentration are plotted in Figure 8a. As can be seen from Figure 8a, when Cu is used as S/D electrodes, the device shows a  $R_C$  of about  $2.2 \times 10^{-1}$  M $\Omega$ . After modified by the 0.1% PEI solution, the  $R_C$  decreases drastically to about 6.1  $\times$  10<sup>-2</sup> M $\Omega$ , which is much lower than that of the unmodified device. The decline in  $R_C$  after PEI modification can be attributed to the decreased W<sub>F</sub> of Cu from 4.65 eV to 4.27 eV, which resulting in a lowered electron injection barrier at the interface of Cu/C<sub>60</sub> and then an improved device performance. With further increasing the concentration of PEI, the  $R_C$  decreases monotonously, and a  $R_C$  of only  $2.7 \times 10^{-3}$  M $\Omega$ is obtained at 0.4%. Interestingly, the average linear region channel conductance of devices with 0 % to 0.4 % PEI is estimated to be 16.7  $\pm$  1.1  $\mu$ S, thus eliminating the doping effect of PEI to C<sub>60</sub>. However, an increased Rc of  $1.0 \times 10^{-3}$  M $\Omega$  is observed with PEI concentration of 0.8%, which can be resulted from the resistive PEI layer. For clarity, the dependence of  $R_C$  on PEI concentration is plotted in the upper inset of Figure 8a. The variation of  $R_C$  with PEI concentration is consistent with the electrical characteristics of the corresponding device. In order to provide a clear picture on the mechanism of improvement in device performance, the band structures at the interfaces of Cu/C<sub>60</sub> before and after 0.4% PEI modification are illustrated in Figure 8b. For C<sub>60</sub>, a LUMO of 4.5 eV is adopted in our present study [60,61,62]. The left part of Figure 8b shows the band structure of  $Cu/C_{60}$  interface without modification, in which  $E_{Vac}$  and  $E_F$  denote the vacuum level and Fermi level, respectively.

Figure 8. (a) Transfer line method (TLM) plots of  $C_{60}$  OTFTs modified by various PEI concentrations and (b) energy level diagrams at the interface of  $Cu/C_{60}$  before (left) and after (right) PEI modification; the inset of (a) shows the relationship between the contact resistance and PEI concentration.

As seen, an electron injection barrier of 0.40 eV is observed between Cu and  $C_{60}$  due to the existence of interface dipole [63], which is then responsible for the poor device performance and the high contact resistance. In contrast, as depicted in the right part of Figure 8b, after modified by PEI, an electron injection favorable band structure is achieved due to the combining effects of reduced  $W_F$  of Cu to 4.28 eV and suppression of interface dipoles. Consequently, obviously enhanced electrical properties as well as drastically decreased  $R_C$  can be expected with the resultant device.

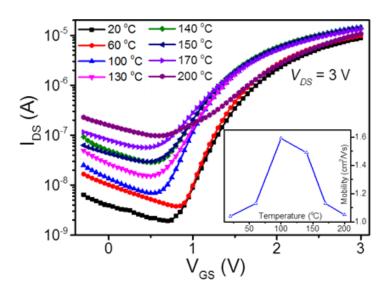

The thermal stability of the above PEI modified device is also characterized and the results are given in Figure 9. To eliminate the influence of oxygen and water vapor in air, the device is encapsulated by a layer of 200 nm CYTOP. As seen, the elevated temperature seems to show no obvious influence on the turn-on voltage of the device. On the other hand, the off-current increases with temperature, which can be due to combined effects of increased conductance of  $C_{60}$  film and gate leakage at higher temperatures. The inset of Figure 9 plots the temperature dependent mobility of the device. Notably, after CYTOP encapsulation, the mobility decreases to about 1.0 cm<sup>2</sup>/Vs, which is presumably due to the residue of CYTOP solvent in the  $C_{60}$  film. The mobility of device increases with the temperature initially until 100 °C, and then declines monotonously. Strikingly, at

temperature as high as 200 °C, our device can still work effectively without any degradation in mobility as compared to the original device, manifesting its outstanding thermal stability. The high thermal stability of the PEI modified device is of great importance to the application of OTFTs in biomedical equipment, in which a high temperature (120 °C) is needed to realize asepsis and prevent infection [64].

Figure 9. Variation of transfer curves of PEI modified devices with temperature; the inset shows the relationship between temperature and mobility.

Low-voltage, flexibility and low-cost are essential prerequisites for large scale application of organic thin film transistors (OTFTs) in future low-end electronics. Previously, we have demonstrated high-performance low-voltage OTFTs with ODPA/ATO dielectric and low-cost Cu S/D electrodes. In this part, we will show that, basing on these findings, high-performance flexible OTFTs can also be realized. The ATO dielectric on Au coated PI substrates was fabricated by spin coating TiO<sub>x</sub> sol (5000 r/min, 40 s) and Al<sub>2</sub>O<sub>y</sub> sol (5000 r/min, 20 s) in sequence, and then baked at 200  $\pm 5$  °C for 3 min, followed by ODPA modification. Figure 10 shows the leakage current density and the capacitance density characteristics of the ODPA/ATO on flexible substrates. As can be seen form Figure 10a, after ODPA modification, the leakage current density can be effectively suppressed by one order of magnitude under bias voltages of  $\pm 3V$ , indicating that the ODPA molecules assemble densely on the surface of alumina in ATO. The large DI H<sub>2</sub>O contact angle (110 °C) of the ODPA/ATO also signifies its low surface energy, which is believed to be critical in enhancing the device properties [65]. Figure 10b shows the frequency dependent capacitance density of ODPA/ATO. A slight increase in capacitance density with decreasing frequency is observed in both ATO and ODPA/ATO, which can be due to the Maxwell-Wagner space charge polarization in the ATO layer [27,66,67]. The obtained  $C_i$  value is 180 nF/cm<sup>2</sup> for ODPA/ATO at 20 Hz, which is in good agreement with the calculated one by using the equation  $1/C_{total}=1/C_{ATO}+1/C_{ODPA}$  [68]. Such a high capacitance density is sufficient to induce adequate charge carriers at a low voltage.

Figure 10. (a) Leakage and (b) frequency dependent capacitance density characteristics of ATO and ODPA/ATO.

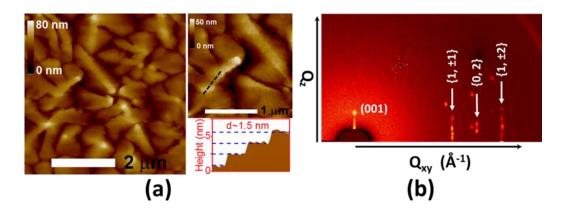

Figure 11a exhibits the AFM image of 30 nm pentacene film deposited on flexible substrate. Typical herringbone structure with feature size of  $\sim 2~\mu m$  can be clearly observed from left one in Figure 11a. In addition, in magnified image, terraces with height of  $\sim 1.5$  nm can be clearly observed, as shown in the upper right one, corresponding to an edge-on configuration. To further explore the crystalline structure and molecular ordering of the deposited pentacene film, the corresponding GIXD pattern is recorded and the result is given in Figure 11b. As seen, the (001) reflection peak along the  $Q_z$  (out of plain) axis can be assigned to the "thin film phase" with a layer spacing of  $\sim 1.54$  nm, which is approximately equal to the up-right standing molecular height [69]. Additionally, the  $\{1, \pm 1\}$ ,  $\{0, 2\}$  and  $\{1, \pm 2\}$  in plane Bragg rod reflections at  $Q_{xy}$  (in plain) positions indicate that the pentacene crystal has a highly oriented 3D herringbone packing structure, as evidenced by many groups [69,70,71]. The "thin film phase" is believed to benefit the charge carrier transport, due to the preferred  $\pi$ -orbital overlap [72].

Figure 11. (a) AFM image of 30 nm pentacene film deposited on ODPA/ATO and the cross-sectional profile along the dark line; (b) the corresponding GIXD pattern.

We have proved the effectiveness of M-Cu as S/D electrodes in pentacene OTFTs. However, one major disadvantage of using Cu as S/D electrodes is the inevitable oxidation of Cu by oxygen species and water in air. To resolve this problem, a An encapsulation layer on M-Cu is employed.

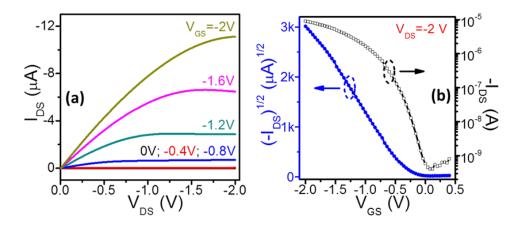

Figure 12 shows the electrical characteristics of flexible pentacene TFT using 10 nm Au encapsulated 30 nm M-Cu (Au/M-Cu) as S/D electrodes. Due to the high capacitance density (180 nF/cm<sup>2</sup>) of the ODPA/ATO system, the device can work perfectly under a low operating voltage of only -2 V. As shown in Figure 12a, the output curves exhibit distinct linear and saturation regions of a typical p-type feature, with a high saturation current on the order of  $10^{-5}$  A under  $V_{GS} = V_{DS} = -2$  V. No obvious leakage can be observed at zero  $V_{DS}$  due to the high quality of the ODPA/ATO system. Figure 12b plots the corresponding transfer curves in saturation region, from which the electronic parameters can be extracted. The device possesses outstanding electronic characteristics, with on/off ratio of  $2 \times 10^4$ ,  $\mu$  of 1.5 cm<sup>2</sup>/Vs,  $V_T$  of -0.4 V and SS of 161 mV/dec. To the best of our knowledge, this obtained mobility value is among the highest ones achieved in flexible pentacene TFTs. The high performance of our flexible pentacene TFT with Au/M-Cu S/D electrodes can be ascribed to the "thin film pahse" of the deposited pentacene film and the potimized electrode/pentacene interface property.

Figure 12. (a) Output and (b) transfer curves of flexible pentacene OTFT.

The mechanical flexibility of the devices is investigated at controlled bending radii along the channel length direction, under either compressive or tensile condition. Figure 13a and b show the relative variation in the normalized  $\mu$  and  $V_T$  of the devices as a function of strain. As can be seen form Figure 13a, in case of compressive strains, the mobility decreases gradually with increasing the strain at first, and then a rapid degradation is observed. A 40% degradation in  $\mu$  is observed at strain of 2.7%, and the  $V_T$  shifts in a small range from -0.55 V to -0.58 V. On the other hand, as shown in Figure 13b, in case of tensile strains, a more drastic degradation in the mobility is observed and only about 10% is preserved at strain of -2.7%, and the  $V_T$  shifts in a larger range from -0.46 V to -0.68V. Yang et al. reported that the mechanical strain could induce phase transitions of pentacene between thin film phase and bulk phase [73]. To investigate the crystal structure variation, XRD patterns of 30 nm pentacene on flexible substrates are recorded under strains of  $\pm 2.7\%$ , and the results are shown in Figure 13c. For the as-deposited pentacene film, the only peak indexed as  $(001)_T$ can be assigned to the thin film phase, with interlayer spacing of about 1.54 nm [74], which is in good agreement with the previous GIXD result. However, under both compressive and tensile strains, another peak shows up, which corresponds to the bulk phase of pentacene with interlayer spacing of 1.45 nm as denoted by (001)<sub>B</sub> in Figure 13c, indicating a phase transition occurs. Further investigations show that the mass fraction of the thin film phase is about 20% in compressive strain (2.7%), while about 14% in tensile strain (-2.7%). The remained higher thin film phase mass fraction

may partly account for the better mechanical flexibility of the OTFTs under compressive strains, since the bulk phase is reported to possess lower intrinsic mobility than the thin film phase [74].

Figure 13. Relative changes in the normalized mobility of the flexible pentacene TFTs as a function of (a) compressive and (b) tensile strains; (c) XRD patterns of 30 nm pentacene film with different strains.

## 4. Conclusion

In summary, we have successfully achieved low-voltage OTFTs by introducing a solution-processed, low-temperature cured high-*k* ATO as the gate dielectric. The ATO based low-voltage CuPc OTFTs exhibit much higher device performance than the traditional 300 nm SiO<sub>2</sub> due to the difference in initial growth of CuPc. The electrical and physical-chemical performance of ATO can be optimized by ODPA modification, featuring in suppressed leakage and surface energy. By using interface engineering, highly improved electrical performance can be obtained in both pentacene and C<sub>60</sub> OTFTs with low-cost *M*-Cu and Cu/PEI S/D electrodes at a low voltage. Furthermore, based on the above findings, flexible pentacene OTFTs with outstanding performance can be realized by employing ODPA/ATO as gate dielectric and Au encapsulated M-Cu as S/D electrodes. Our studies can further advance the development of large scale application of organic electronics featured with low-cost and low-voltage.

# Acknowledgments

The work is in part supported by Research Grants Council of Hong Kong, particularly, via Grant Nos. AoE/P-03/08, CUHK4179/10E, N\_CUHK405/12, T23-407/13-N, AoE/P-02/12, and CUHK Group Research Scheme. We would like to thank the National Science Foundation of China for the support, particularly, via Grant Nos. 61229401 and 61106093.

# **Conflict of Interest**

The authors report no conflict of interests in this research.

## References

- 1. Halik M, Klauk H, Zschieschang U, et al. (2004) Low-voltage organic transistors with an amorphous molecular gate dielectric. *Nature* 431: 963–966.

- 2. Moon H, Zeis R, Borkent E, et al. (2004) Synthesis, crystal structure, and transistor performance of tetracene derivatives. *J Am Chem Soc* 126: 15322–15223.

- 3. Jung B., Lee K, Sun J, et al. (2010) Air-operable, high-mobility organic transistors with semifluorinated side chains and unsubstituted naphthalenetetracarboxylic diimide cores: high mobility and environmental and bias stress stability from the perfluorooctylpropyl side chain. *Adv Funct Mater* 20: 2930–2944.

- 4. Dickey K, Anthony J, Loo Y, (2006) Improving organic thin-Film transistor performance through solvent-vapor annealing of solution-processable triethylsilylethynyl anthradithiophene. *Adv Mater* 18: 1721–1726.

- 5. Coropceanu V, Cornil J, Demetrio A, et al. (2007) Charge transport in organic semiconductors. *Chem Rev* 107: 926–952.

- 6. Li W, Auciello O, Premnath R, et al. (2010) Giant dielectric constant dominated by Maxwell-Wagner relaxation in Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> nanolaminates synthesized by atomic layer deposition. *Appl Phys Lett* 96: 162907.

- 7. Lee J, Kim J, Im S, et al. (2003) Pentacene thin-film transistors with Al<sub>2</sub>O<sub>3+x</sub> gate dielectric films deposited on indium-tin-oxide glass. *Appl Phys Lett* 83: 2689.

- 8. Maunoury C, Dabertrand K, Martinez E, et al. (2007) Chemical interface analysis of as grown HfO<sub>2</sub> ultrathin films on SiO<sub>2</sub>. *J Appl Phys* 101: 034112.

- 9. Di C, Yu G, Liu Y, et al. (2006) High-performance low-cost organic field-effect transistors with chemically modified bottom electrodes. *J Am Chem Soc* 128: 16418–16419.

- 10. Di C, Yu G, Liu Y, et al. (2008) High-performance organic field-effect transistors with low-cost copper electrodes. *Adv Mater* 20: 1286–1290.

- 11. Di C, Liu Y, Yu G, et al. (2009) Interface engineering: an effective approach toward high-performance organic field-effect transistors. *Acc Chem Res* 42: 1573–1583.

- 12. Ma H, Yip H, Huang F, et al. (2010) Interface engineering for organic electronics. *Adv Funct Mater* 20: 1371–1388.

- 13. Chua L, Zaumseil J, Chang J, et al. (2005) General observation of n-type field-effect behaviour in organic semiconductors. *Nature* 434: 194–199.

- 14. Frank M, Sayan S, Dörmann S, et al. (2004) Hafnium oxide gate dielectrics grown from an alkoxide precursor: structure and defects. *J Mater Sci Eng B* 109: 6–10.

- 15. Lu Y, Lee W, Lee H, et al. (2009) Low-voltage organic transistors with titanium oxide/polystyrene bilayer dielectrics. *Appl Phys Lett* 94: 113303.

- 16. Fleischli F, Suarez S, Schaer M, et al. (2010) Organic thin-film transistors: the passivation of the dielectric-pentacene interface by dipolar self-assembled monolayers. *Langmuir* 26: 15044–15049.

- 17. Wu W, Liu Y, Wang Y, et al. (2008) High-performance, low-operating-voltage organic field-effect transistors with low pinch-off voltages. *Adv Funct Mater* 18: 810–815.

- 18. Tang M, Okamot T, Bao Z, (2006) High-performance organic semiconductors: asymmetric linear acenes containing sulphur. *J Am Chem Soc* 128: 16002–16003.

- 19. Acton O, Osaka I, Ting G, et al. (2009) Phosphonic acid self-assembled monolayer and

- amorphous hafnium oxide hybrid dielectric for high performance polymer thin film transistors on plastic substrates. *Appl Phys Lett* 95: 113305.

- 20. Gao W, Dickinson L, Grozinger C, et al. (2009) Self-assembled monolayers of alkylphosphonic acids on metal oxides. *Langmuir* 12: 6429–6435.

- 21. Ma H, Acton O, Ting G, et al. (2008) Low-voltage organic thin-film transistors with  $\pi$ - $\sigma$ -phosphonic acid molecular dielectric monolayers. *Appl Phys Lett* 92: 113303.

- 22. McElwee J, Helmy R, Fadeev A, et al. (2005) Thermal stability of organic monolayers chemically grafted to minerals. *J Colloid Interface Sci* 285: 551–556.

- 23. Acton O, Ting G, Ma H, et al. (2008)  $\pi$ -σ-Phosphonic acid organic monolayer/sol-gel hafnium oxide hybrid dielectrics for low-voltage organic transistors. *Adv Mater* 20: 3697–3701.

- 24. Lu X, Minari T, Kumatani A. et al. (2011) Effect of air exposure on metal/organic interface in organic field-effect transistors. *Appl Phys Lett* 98: 243301.

- 25. Di C, Yu G, Liu Y, et al. (2008) Efficient modification of Cu electrode with nanometer-sized copper tetracyanoquinodimethane for high performance organic field-effect transistors. *Phys Chem Chem Phys* 10: 2302–2307.

- 26. Gu W, Jin W, Wei B, at al. (2010) High-performance organic field-effect transistors based on copper/copper sulphide bilayer source-drain electrodes. *Appl Phys Lett* 97: 243303.

- 27. Su Y, Wang C, Xie W, et al. (2011) Low-voltage organic field-effect transistors (OFETs) with solution-processed metal-oxide as gate dielectric. *ACS Appl Mater Interfaces* 3: 4662–4667.

- 28. Su Y, Xie W, Li Y, et al. (2013) A low-temperature, solution-processed high-k dielectric for low-voltage, high-performance organic field-effect transistors (OFETs). *J Phys D Appl Phys* 46: 095105.

- 29. Su Y, Ouyang M, Liu P, et al. (2013) Insights into the interfacial properties of low-voltage CuPc field-effect transistor. *ACS Appl Mater Interfaces* 5: 4960–4965.

- 30. Su Y, Wang M, Xie F, et al. (2013) *In situ* modification of low-cost Cu electrodes for high-performance low-voltage pentacene thin film transistors (TFTs). *Org Electron* 14: 775–781.

- 31. Su Y, Xie W, Xu J, (2014) Facile modification of Cu source-drain (S/D) electrodes for high-performance, low-voltage n-channel organic thin film transistors (OTFTs) based on C60. *Org Electron* 15: 3259–3267.

- 32. Su Y, Jiang J, Ke N, et al. (2013) Low-voltage flexible pentacene thin film transistors with solution-processed dielectric and low-cost source-drain (S/D) electrodes. *J Mater Chem C* 1: 2585–2592.

- 33. Forrest S, (1997) Ultrathin organic films grown by organic molecular beam deposition and related techniques. *Chem Rev* 97: 1793–1896.

- 34. Yang S, Shin K, Par C, (2015) The effect of gate-dielectric surface energy on pentacene morphology and organic field-effect transistor characteristics. *Adv Funct Mater* 15: 1806–1814.

- 35. Gao J, Xu J, Zhu M, et al. (2007) Thickness dependence of mobility in CuPc thin film on amorphous SiO<sub>2</sub> substrate. *J Phys D Appl Phys* 40: 5666–5669.

- 36. Qi Q, Yu A, Wang L, et al. (2010) Behavior of pentacene initial nucleation on various dielectrics and its effect on carrier transport in organic field-effect transistor. *J Nanosci Nanotechnol* 10: 7103–7107.

- 37. Chung Y, Verploegen E, Vailionis A, et al. (2011) Controlling electric dipoles in nanodielectrics and its applications for enabling air-stable n-channel organic transistors. *Nano Lett* 11: 1161–1165.

- 38. Nakamura M, Goto N, Ohashi N, et al. (2005) Potential mapping of pentacene thin-film transistors using purely electric atomic-force-microscope potentiometry. *Appl Phys Lett* 86: 122112.

- 39. Wang S, Minari T, Miyadera T, et al. (2007) Bias stress instability in pentacene thin film transistors: contact resistance change and channel threshold voltage shift. *Appl Phys Lett* 91: 203508.

- 40. Kim Y, Jeon D, (2010) Effect of deposition temperature on the morphology and contact resistance of Au on pentacene. *J Appl Phys* 108: 016101.

- 41. Diao L, Frisbie C, Schroepfer D, et al. (2007) Electrical characterization of metal/pentacene contacts. *J Appl Phys* 101: 014510.

- 42. Zaumseil J, Baldwin K, Rogers J, (2003) Contact resistance in organic transistors that use source and drain electrodes formed by soft contact lamination. *J Appl Phys* 93: 6117–6124.

- 43. Watkins N, Yan L, Gao Y, (2002) Electronic structure symmetry of interfaces between pentacene and metals. *Appl Phys Lett* 80: 4384.

- 44. Kang S, Yi Y, Kim C, et al. (2006) Energy level diagrams of C60/pentacene/Au and pentacene/C60/Au. *Synth Met* 156: 32–37.

- 45. Zhang D, Liu Y, Liu Y, et al. (2004) The electrical properties and the interfaces of Cu<sub>2</sub>O/ZnO/ITO p-i-n heterojunction. *Physica B: Cond Mat* 351: 178–183.

- 46. Tseng C, Cheng Y, Lee M, et al. (2007) Study of anode work function modified by self-assembled monolayers on pentacene/fullerene organic solar cells. *Appl Phys Lett* 91: 233510.

- 47. Zhou Y, Fuentes-Hernandez C, Shim J, et al. (2012) A universal method to produce low-work function rlectrodes for organic electronics. *Science* 336: 327–332.

- 48. Yu Y, Zhao Y, Ryu S, et al. (2009) Tuning the graphene work function by electric field effect. *Nano Lett* 9: 3430–3434.

- 49. Rentenberger S, Vollmer A, Zojer E, (2006) UV/ozone treated Au for air-stable, low hole injection barrier electrodes in organic electronics. *J Appl Phys* 100: 053701.

- 50. Scheinert S, Grobosch M, Paasch G, et al. (2012) Contact characterization by photoemission and device performance in P3HT based organic transistors. *J Appl Phys* 111: 064502.

- 51. Shibata K, Ishikawa K, Takezoe H, et al. (2008) Contact characterization by photoemission and device performance in P3HT based organic transistors. *Appl Phys Lett* 92: 023305.

- 52. Kumatani A, Li Y, Darmawan P, et al. (2013) On practical charge injection at the metal/organic semiconductor interface. *Sci Rep* 3: 1026.

- 53. Heimel G, Romaner L, Bredas J, et al. (2006) Interface energetics and level alignment at covalent metal-molecule Junctions:  $\pi$ -conjugated thiols on gold. *Phys Rev Lett* 96: 196806.

- 54. Heimel G, Romaner L, Zojer E, et al. (2008) The interface energetics of self-assembled monolayers on metals. *Acc Chem Res* 41: 721–729.

- 55. Li H, Paramonov P, Bredas J, (2010) Theoretical study of the surface modification of indium tin oxide with trifluorophenyl phosphonic acid molecules: impact of coverage density and binding geometry. *J Mater Chem* 20: 2630–2637.

- 56. Yang R, Park J, Colesniuc C, et al. (2009) Analyte chemisorption and sensing on *n* and *p*-channel copper phthalocyanine thin-film transistors. *J Chem Phys* 130: 164703.

- 57. Ma H, Acton O, Hutchins D, et al. (2012) Multifunctional phosphonic acid self-assembled monolayers on metal oxides as dielectrics, interface modification layers and semiconductors for low-voltage high-performance organic field-effect transistors. *Phys Chem Chem Phys* 14:

- 14110-14126.

- 58. Acton O, Ting G, Ma H, et al. (2008) Low-voltage high-performance C60 thin film transistors via low-surface-energy phosphonic acid monolayer/hafnium oxide hybrid dielectric. *Appl Phys Lett* 93: 083302.

- 59. Colleaux F, Ball J, Wobkenberg P, et al. (2011) Bias-stress effects in organic field-effect transistors based on self-assembled monolayer nanodielectrics. *Phys Chem Chem Phys* 13: 14387–14393.

- 60. Nanditha D, Dissanayake M, Hatton R, (2007) Operation of a reversed pentacene-fullerene discrete heterojunction photovoltaic device. *Appl Phys Lett* 90: 113505.

- 61. Chu C, Shrotriya V, Li G, et al. (2006) Tuning acceptor energy level for efficient charge collection in copper-phthalocyanine-based organic solar cells. *Appl Phys Lett* 88: 153504.

- 62. Chu C, Sung C, Kekuda D, et al. (2009) Flexible fullerene field-effect transistors fabricated through solution processing. *Adv Mater* 21: 4845–4849.

- 63. Ishii H, Hayashi N, Ito E, et. (2004) Kelvin probe study of band bending at organic semiconductor/metal interfaces: examination of Fermi level alignment. *Phys Stat Sol A* 201: 1075–1094.

- 64. Kuribara K, Wang H, Uchiyama N, et al. (2012) Organic transistors with high thermal stability for medical applications. *Nat Commun* 3: 723.

- 65. Kraus M, Richler S, Opitz A, et al. (2010) High-mobility copper-phthalocyanine field-effect transistors with tetratetracontane passivation layer and organic metal contacts. *J Appl Phys* 107: 094503.

- 66. Ramanathan S, Park C, McIntyre P, (2002) Electrical properties of ultrathin zirconia films grown by UV ozone oxidation. *J Appl Phys* 91: 4521–4527.

- 67. Gonon P, El Kamel F, (2007) Dielectric response of Cu/amorphous BaTiO<sub>3</sub>/Cu capacitors. *J Appl Phys* 101: 073901.

- 68. Klauk H, Zschieschang U, Pflaum J, et al. (2007) Ultralow-power organic complementary circuits. *Nature* 445: 745–748.

- 69. Kim S, Yoon W, Jang M, et al. (2012) Damage-free hybrid encapsulation of organic field-effect transistors to reduce environmental instability. *J Mater Chem* 22: 7731–7738.

- 70. Yang H, Kim S, Yang L, et al. (2007) Pentacene nanostructures on surface-hydrophobicity-controlled polymer/SiO<sub>2</sub> bilayer gate-dielectrics. *Adv Mater* 19: 2868–2872.

- 71. Yang H, Yang L, Ling M, et al. (2008) Aging susceptibility of terrace-like pentacene films. *J Phys Chem C* 112: 16161–16165.

- 72. Nabok D, Puschnig P, Ambrosch-Draxl C, et al. (2007) Crystal and electronic structures of pentacene thin films from grazing-incidence x-ray diffraction and first-principles calculations. *Phys Rev B* 76: 235322.

- 73. Yang C, Yoon J, Kim S, et al. Bending-stress-driven phase transitions in pentacene thin films for flexible organic field-effect transistors. *Appl Phys Lett* 92: 243305.

- 74. Kang S, Noh Y, Baeg K, et al. (2008) Effect of rubbed polyimide layer on the field-effect mobility in pentacene thin-film transistors. *Appl Phys Lett* 92: 052107.

© 2015 Yaorong Su, et al., licensee AIMS Press. This is an open access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0)